智融SW630X移动电源PCB 设计指南

四层板设计:第一层(顶层)用于走线和地;第二层(内层)为走线和电源层;第三层(内层)是完整的地层(可能有模拟地和数字地);第四层(底层)用于走线和地。第二层和第三层可根据主要元件的布局层面确定,其紧邻层为地。

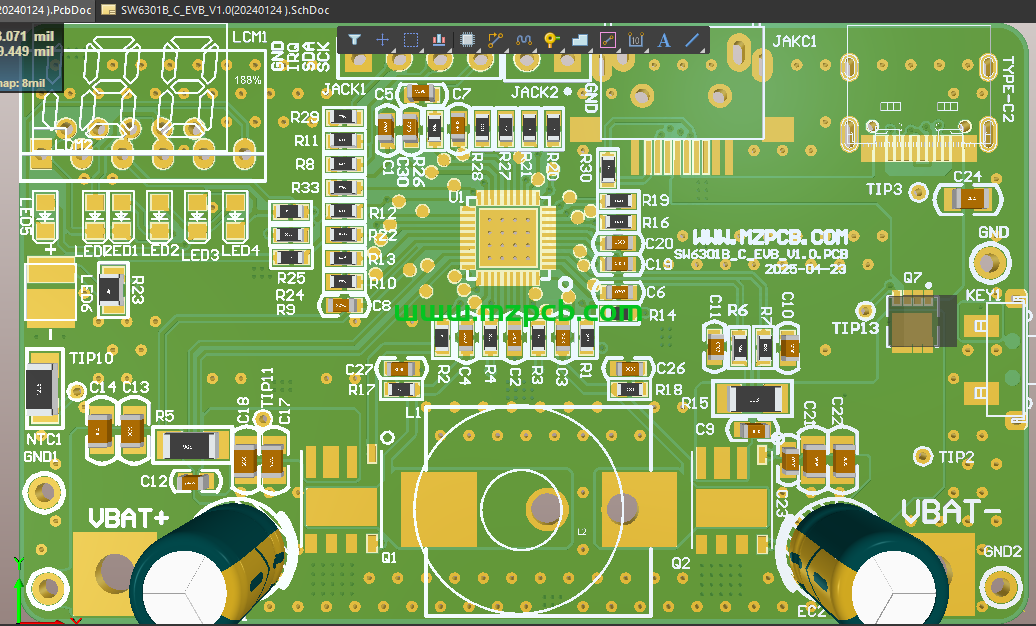

元件布局

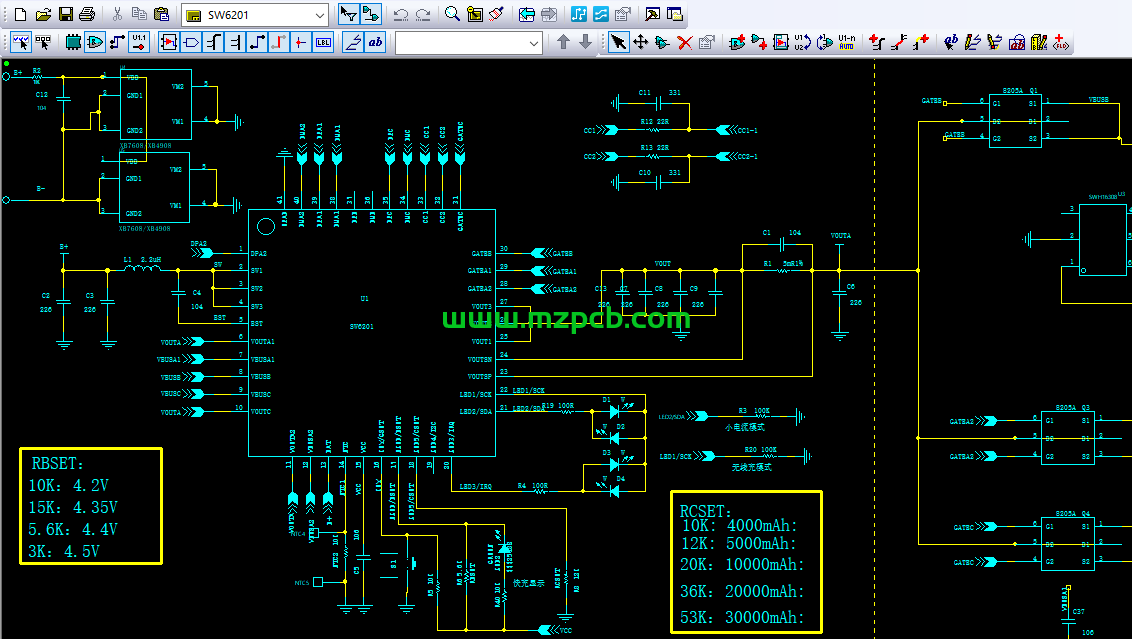

电源部分:将 SW630X 芯片与功率电感尽可能放在 PCB 的同一边,且电感要靠近芯片的 SW 脚,走线宽度不小于 0.6mm。电源输入端的滤波电容建议采用钽电容,如 4.7μF 或 10μF,或使用 ESR 值低的电容;功率电感输出端需连接 0.1μF 和 10μF 的电容,且这些电容要尽可能靠近芯片输出端,距离不超过 4mm,0.1μF 的退耦电容最好放在 10μF 电容的前面。

SW630X_PCB 设计指南:

SW630X_PCB 设计指南:

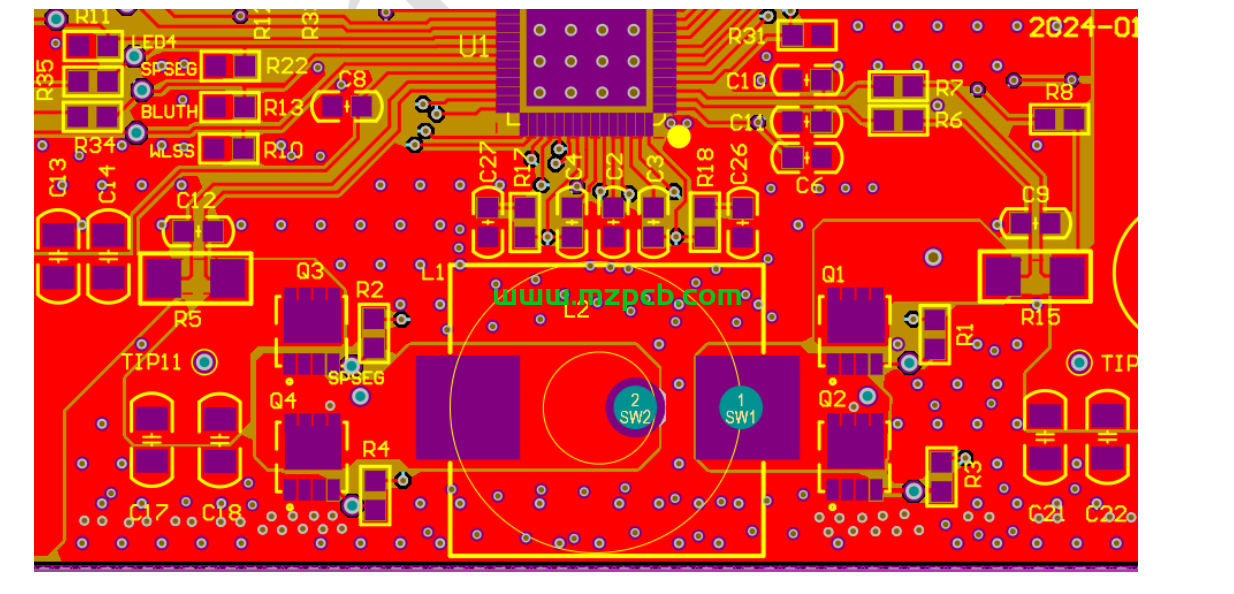

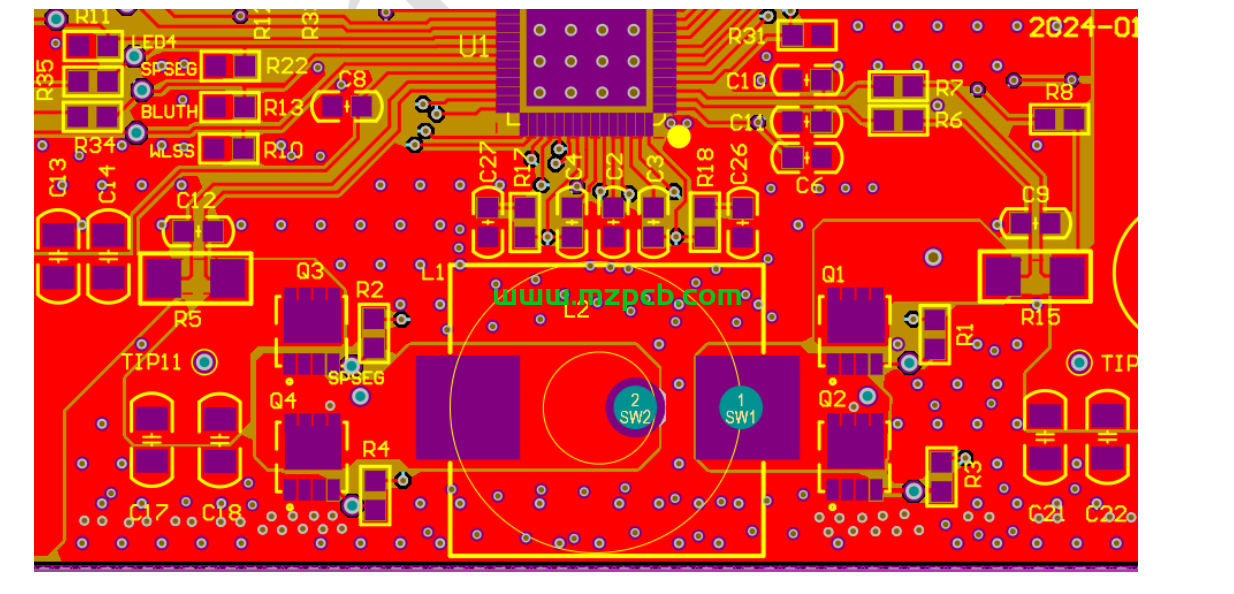

H 桥开关 NMOS 的摆放:

(1) H 桥功率 MOS 管和电感为主要发热器件,适当远离芯片,要加强散热,建议 Q1~Q4 开关 MOS 管摆放在同一侧,摆放建议如上图,SW1、SW2 面积尽量小,以减少辐射;

(1) H 桥功率 MOS 管和电感为主要发热器件,适当远离芯片,要加强散热,建议 Q1~Q4 开关 MOS 管摆放在同一侧,摆放建议如上图,SW1、SW2 面积尽量小,以减少辐射;

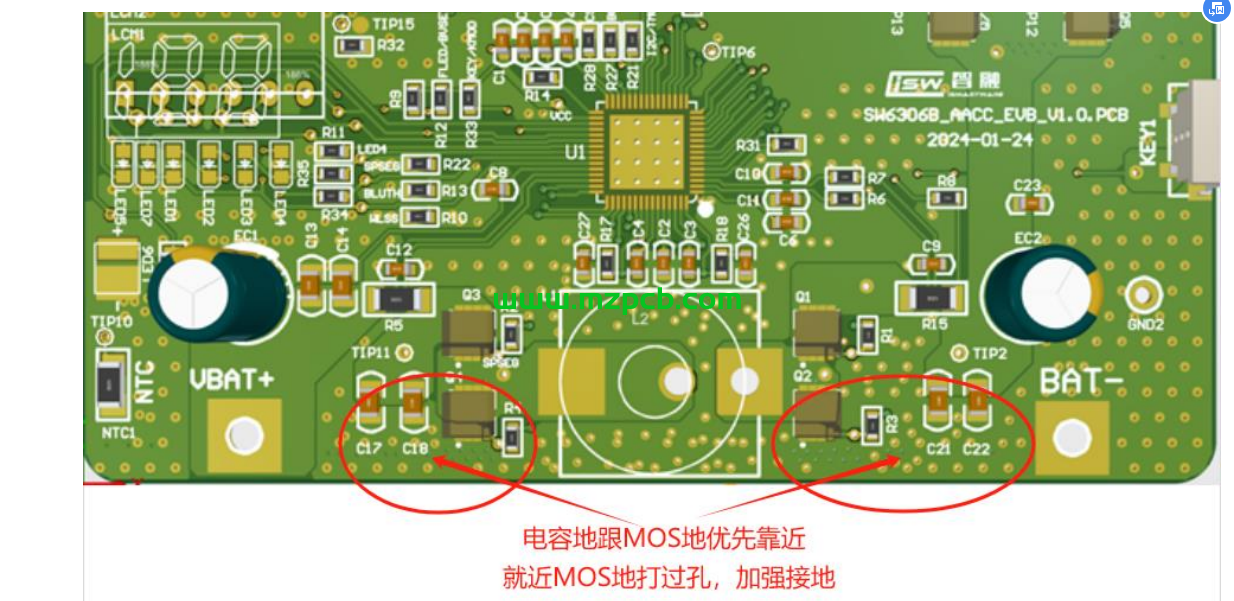

(2) 开关 MOS 下管 MOS(Q4、Q2)接地要良好,保持足够的地线,靠近管脚要多打些过孔,让开关回路阻抗尽量的少,这样可以提高效率及减少 EMI 辐射,让芯片工作可靠稳定;

(3) 4 根 GATE 驱动串联的电阻,建议靠近 MOS 端摆放,走线建议 0.25mm(10mil)线宽以上,尽量避开电感位置走线,实在避不开的需要用中间层完整地线隔开;

(4) H 桥开关 MOS 和电感位置下层需要有完整的地线层,保持完整的地线屏蔽层;

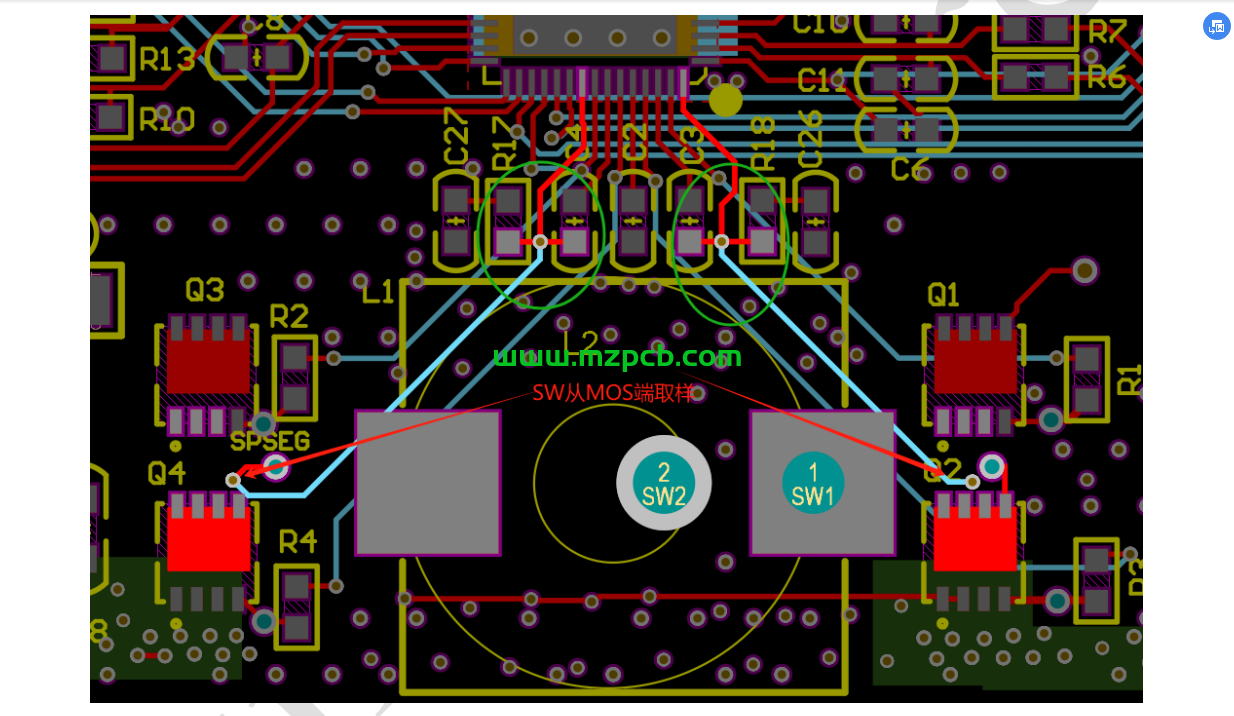

(5) SW1、SW2 反馈线靠近下管 MOS 管脚取样(Q4、Q2),否则影响尖峰电流采样精度,

见下图:

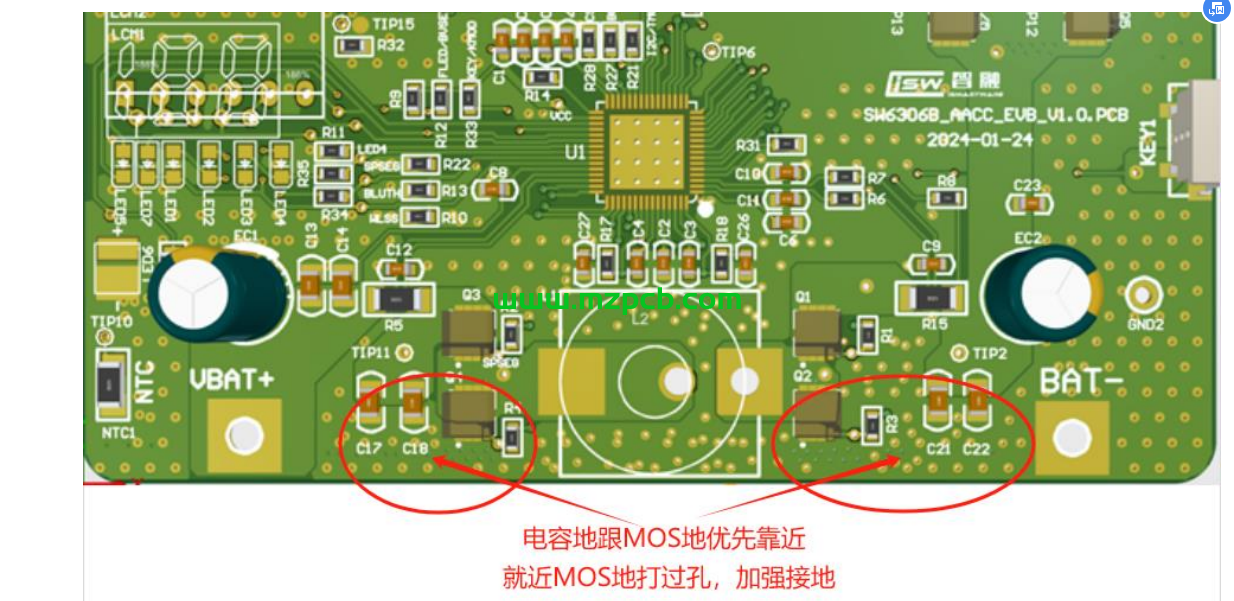

输入输出滤波电容摆放:

(1) 输入输出瓷片电容及固态电容 GND 端优先靠近功率下管的 GND 连接,路径尽可能短。

电流采样电阻注意事项:

(1) 电流采样电阻上的引线须采用开尔文接法,从电阻焊盘向里拉出,单独引线 CAP_VBAT、CAN_VBAT 引脚,中间不要引线到其它地方,同样 VBUS 端采样电阻通过电阻直接引线到 CAP_VBUS、CSN_VBUS 引脚,线宽为 8mil 或 10mil 即可,与采样电阻并联的 0.1uF电容靠近采样电阻摆放,采样线尽量用地线包裹,避免受到干扰,如下图:地线

吸收 RC 电路的摆放:(1) SW1、SW2 吸收电路 RC(建议 4.7R、1nF),尽量靠近 SW 反馈线放置,布局注意减少 SW到地的环路面积,如果不过认证,可以 NC,减少元件减低 BOM 成本及提高电路效率。

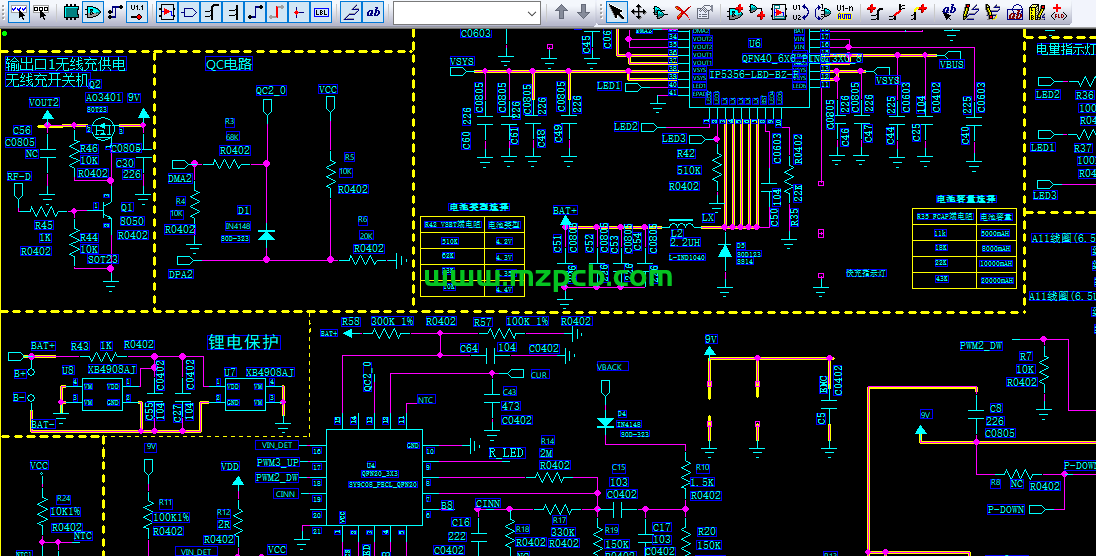

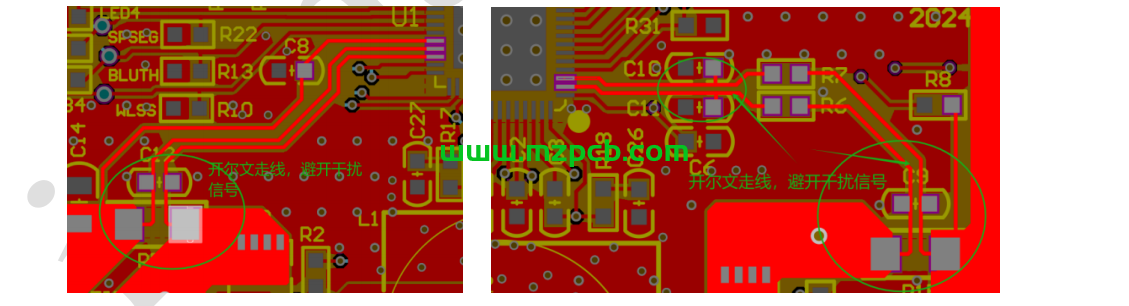

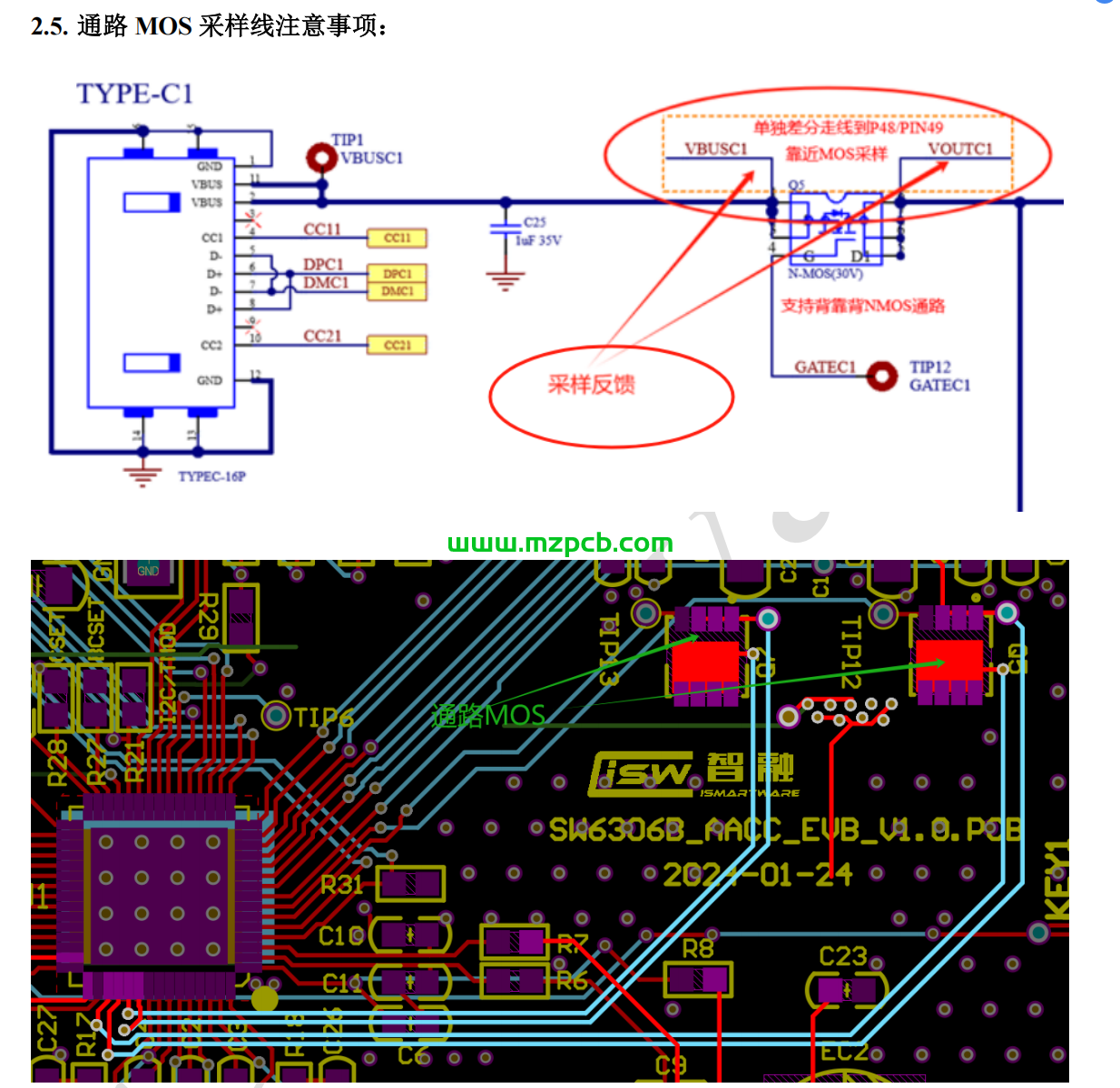

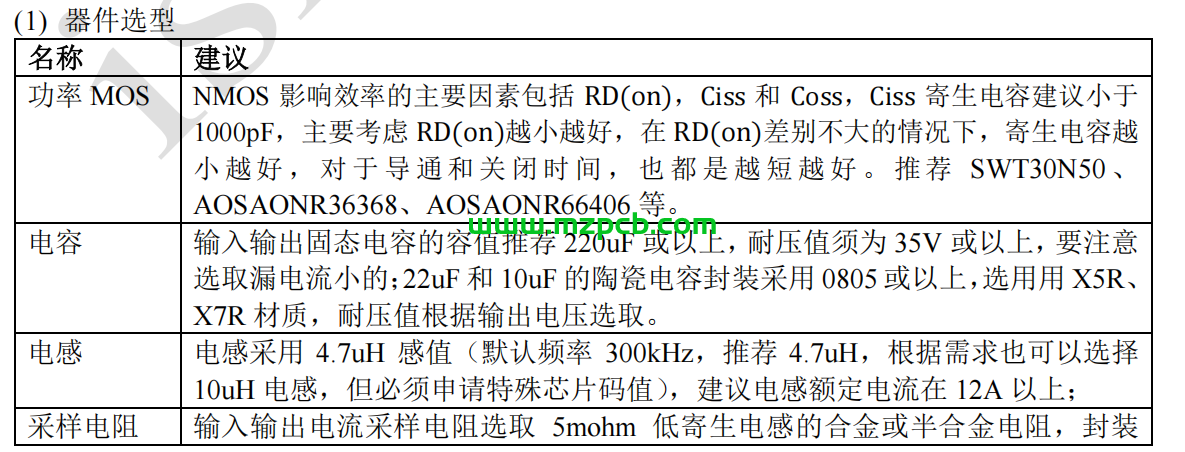

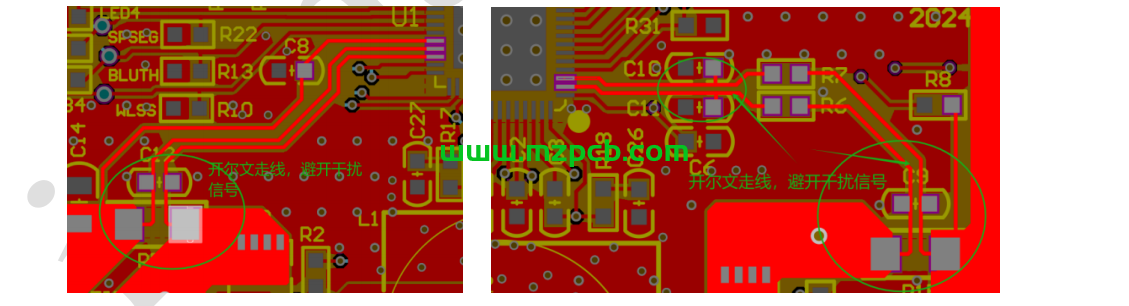

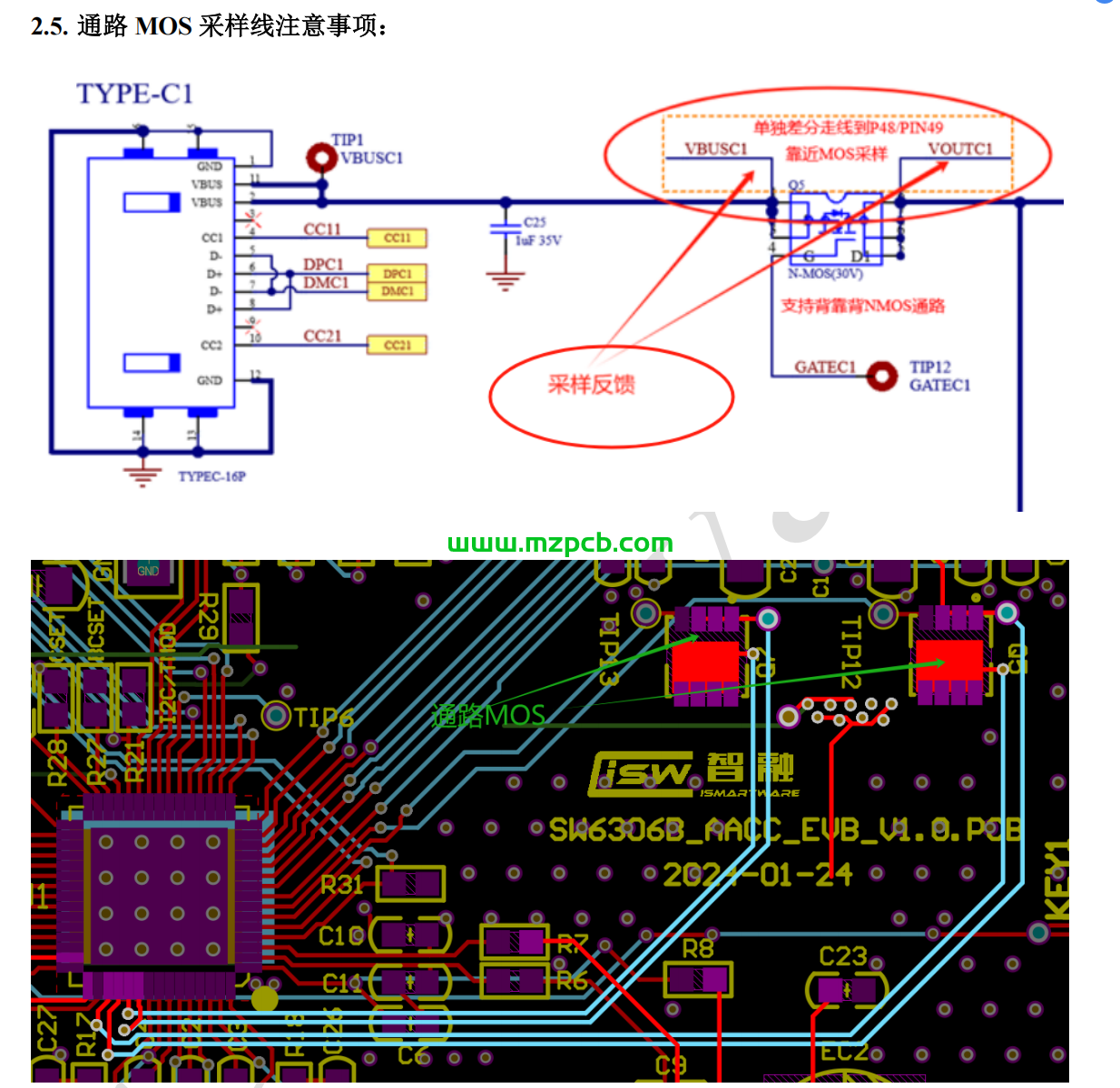

1、每个通路 MOS 的反馈线复用端口负载电流采样功能,走线不好会导致不能轻载关闭输出,如 C1 口 VBUSC1、VOUTC1 必须从通路 MOS 引脚取样,平行单独到对应的芯片 PIN 脚,平行走线,避开干扰信号,特别是 VOUTC 因跟其它端口同网络,各通路 MOS 到芯片 PIN 脚采样线必须对应独立分开,如上图;

1、每个通路 MOS 的反馈线复用端口负载电流采样功能,走线不好会导致不能轻载关闭输出,如 C1 口 VBUSC1、VOUTC1 必须从通路 MOS 引脚取样,平行单独到对应的芯片 PIN 脚,平行走线,避开干扰信号,特别是 VOUTC 因跟其它端口同网络,各通路 MOS 到芯片 PIN 脚采样线必须对应独立分开,如上图;

2、VBUSC、VBUSA 等端口网络线还有设备插入触发开机检测的功能,需要避开 SW、I2C 的SCK 等时钟线的强干扰,避免误触发。

DPDM 的走线注意事项:

每个通路的 DPDM 信号线因默认开启了 DM 触发开机的功能,且灵敏度极高,走线的时候需要避开 SW,I2C 的 SCK 等脉冲干扰信号,避免误触发。其它 PIN 脚走线注意事项

(1) VCC、VDRV、COMP1、COMP2 电容尽量靠近芯片摆放,电容地端放过孔加强与芯片 EPAD的连接,降低干扰,让芯片稳定工作;

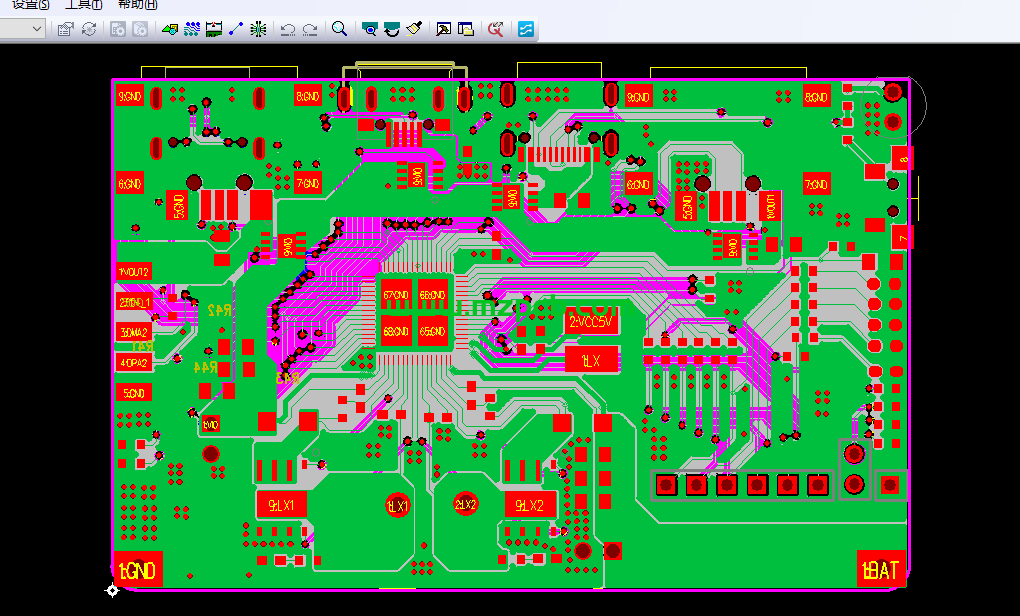

(2) VBUS、SW1、SW2、BAT+、GND 为功率走线,走线尽量宽,最好铺铜,宽度不小于 80mil;SW 的走线要尽可能短,尽量不要换层,大电流网络走线换层时至少 12 个过孔,尽量多打过孔,但要同时考虑底层地的完整性,方便散热;

(3) 过孔的数量根据换层时过电流大小、散热 PAD 的大小而定。VBUS、SW1、SW2、BAT+、GND 换层时推荐打 12 个以上过孔,其他空余空间建议多打过孔,加强底层与顶层的连接,帮助散热;

(4) 一般信号走线(不走大电流)建议线宽 0.2mm(8mil)或 0.25mm(10mil),芯片 HD1、LD1、SW1、HD2、LD2、SW2 引脚到功率元件至少保持 0.25mm(10mil)以上的宽度;

(5) 由于电感所处信号翻转频率较高,容易影响其他信号线,所以电感底部尽量不走线,确实要走线,也用中间层地线隔离,走第三层或第四层;

(6) VBUS、VBAT 的退耦电容靠近芯片摆放,电容端打孔跟芯片 EPAD 地加强连接,见下图:

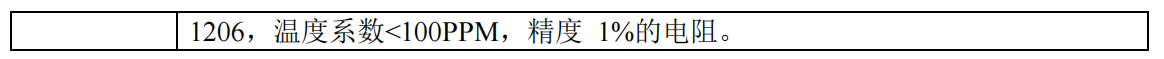

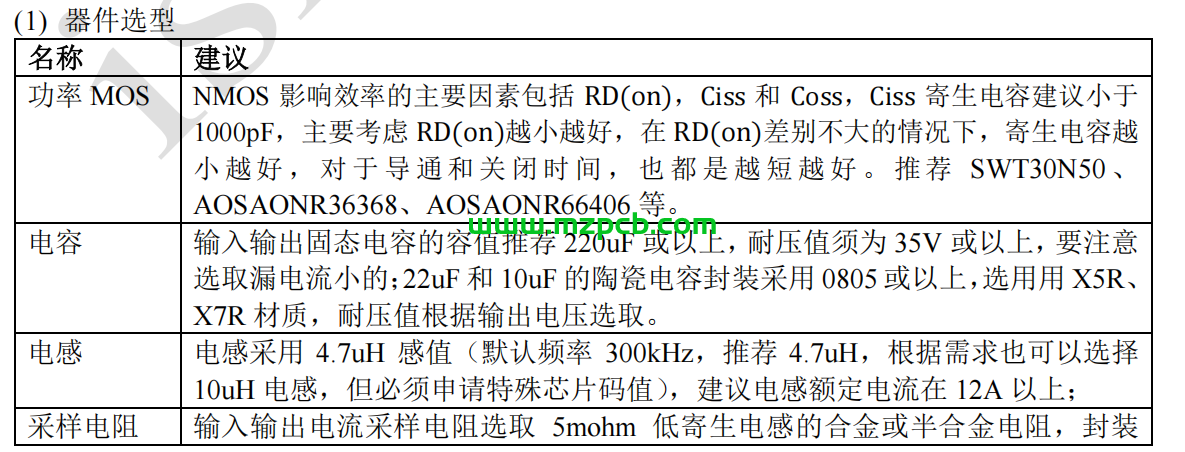

SW630X 器件选型

H 桥开关 NMOS 的摆放:

输入输出滤波电容摆放:

(1) 输入输出瓷片电容及固态电容 GND 端优先靠近功率下管的 GND 连接,路径尽可能短。

电流采样电阻注意事项:

(1) 电流采样电阻上的引线须采用开尔文接法,从电阻焊盘向里拉出,单独引线 CAP_VBAT、CAN_VBAT 引脚,中间不要引线到其它地方,同样 VBUS 端采样电阻通过电阻直接引线到 CAP_VBUS、CSN_VBUS 引脚,线宽为 8mil 或 10mil 即可,与采样电阻并联的 0.1uF电容靠近采样电阻摆放,采样线尽量用地线包裹,避免受到干扰,如下图:地线

吸收 RC 电路的摆放:(1) SW1、SW2 吸收电路 RC(建议 4.7R、1nF),尽量靠近 SW 反馈线放置,布局注意减少 SW到地的环路面积,如果不过认证,可以 NC,减少元件减低 BOM 成本及提高电路效率。

1、每个通路 MOS 的反馈线复用端口负载电流采样功能,走线不好会导致不能轻载关闭输出,如 C1 口 VBUSC1、VOUTC1 必须从通路 MOS 引脚取样,平行单独到对应的芯片 PIN 脚,平行走线,避开干扰信号,特别是 VOUTC 因跟其它端口同网络,各通路 MOS 到芯片 PIN 脚采样线必须对应独立分开,如上图;

1、每个通路 MOS 的反馈线复用端口负载电流采样功能,走线不好会导致不能轻载关闭输出,如 C1 口 VBUSC1、VOUTC1 必须从通路 MOS 引脚取样,平行单独到对应的芯片 PIN 脚,平行走线,避开干扰信号,特别是 VOUTC 因跟其它端口同网络,各通路 MOS 到芯片 PIN 脚采样线必须对应独立分开,如上图;2、VBUSC、VBUSA 等端口网络线还有设备插入触发开机检测的功能,需要避开 SW、I2C 的SCK 等时钟线的强干扰,避免误触发。

DPDM 的走线注意事项:

每个通路的 DPDM 信号线因默认开启了 DM 触发开机的功能,且灵敏度极高,走线的时候需要避开 SW,I2C 的 SCK 等脉冲干扰信号,避免误触发。其它 PIN 脚走线注意事项

(1) VCC、VDRV、COMP1、COMP2 电容尽量靠近芯片摆放,电容地端放过孔加强与芯片 EPAD的连接,降低干扰,让芯片稳定工作;

(2) VBUS、SW1、SW2、BAT+、GND 为功率走线,走线尽量宽,最好铺铜,宽度不小于 80mil;SW 的走线要尽可能短,尽量不要换层,大电流网络走线换层时至少 12 个过孔,尽量多打过孔,但要同时考虑底层地的完整性,方便散热;

(3) 过孔的数量根据换层时过电流大小、散热 PAD 的大小而定。VBUS、SW1、SW2、BAT+、GND 换层时推荐打 12 个以上过孔,其他空余空间建议多打过孔,加强底层与顶层的连接,帮助散热;

(4) 一般信号走线(不走大电流)建议线宽 0.2mm(8mil)或 0.25mm(10mil),芯片 HD1、LD1、SW1、HD2、LD2、SW2 引脚到功率元件至少保持 0.25mm(10mil)以上的宽度;

(5) 由于电感所处信号翻转频率较高,容易影响其他信号线,所以电感底部尽量不走线,确实要走线,也用中间层地线隔离,走第三层或第四层;

(6) VBUS、VBAT 的退耦电容靠近芯片摆放,电容端打孔跟芯片 EPAD 地加强连接,见下图:

SW630X 器件选型

本文地址:https://mzpcb.com/html/42.html

联系我们:QQ:297325108 QQ群:9323379

在线留言:在线留言板 留言不需要注册会员,可以留言建议或者需要咨询的地方。

版权声明:本文为原创文章或转载,遵循[CC 4.0 BY-SA]版权协议,转载请附上原文出处链接。